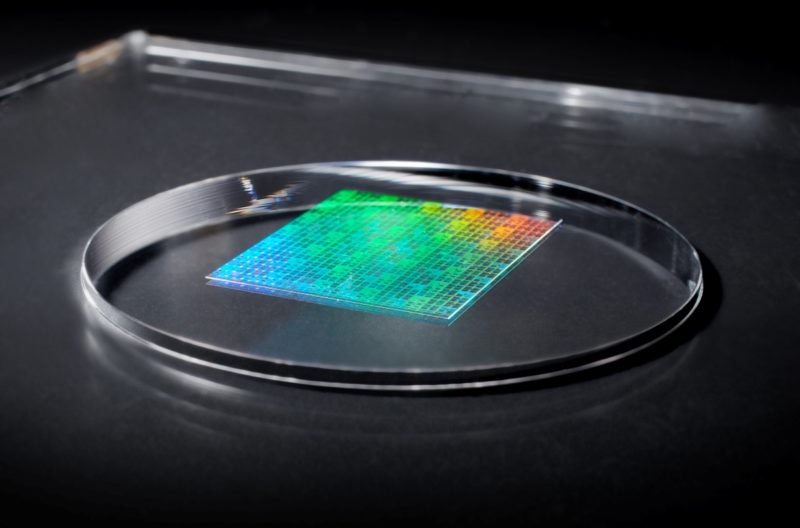

大日本印刷株式會社 (DNP) 近日宣佈,成功開發出電路線寬為 10 奈米的 NIL 奈米壓印技術,可用於相當於 1.4 奈米等級的邏輯半導體電路圖形化。公司表示,該產品針對智慧型手機、資料中心、NAND Flash 等應用場景中先進邏輯晶片的微型化需求,目前已啟動客戶評估工作,計畫於 2027 年開始量產。DNP 同時提出,力爭在 2030 財年將奈米壓印相關業務的營收提升 40 億日元。

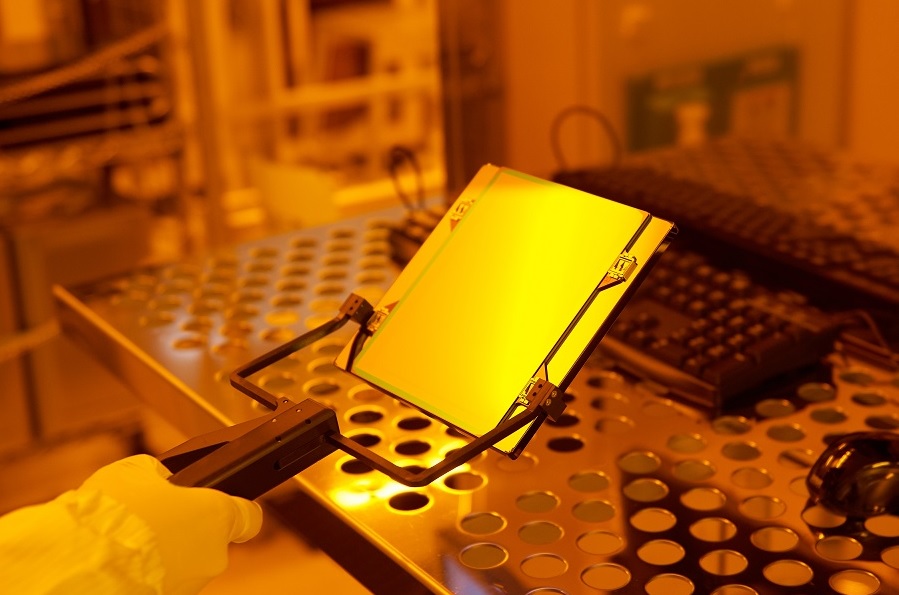

DNP 指出,隨著終端設備性能持續提升,市場對更先進製程邏輯半導體的需求不斷擴大,推動採用極紫外 (EUV) 曝光生產技術的演進。但 EUV 在生產線建設和曝光過程中需要龐大金額的投資,並且有高耗能與環境負荷的問題。因此,自 2003 年起,DNP 開始持續研發奈米壓印技術,通過將電路圖形直接壓印到基板材料上,為製造商在部分製程技術環節上降低曝光能耗、優化成本結構提供了新的技術路徑。

此次推出的 10 奈米線寬 NIL 奈米壓印技術,可在部分圖形化環節上替代 EUV 曝光,為尚未導入 EUV 曝光設備生產線的半導體製造商提供先進邏輯製程的另一個選項。DNP 表示,透過向客戶供應奈米壓印技術,有望在保持圖形精度和線寬控制的前提下,擴大先進製程圖形化的製程選擇空間,協助客戶在製造成本和環境負荷之間取得平衡。公司認為,隨著邏輯元件持續向更精細線寬演進,奈米壓印製程在部分節點可能具備一定經濟性優勢。

而在具體製程技術上,DNP 導入自對準雙重成像 (SADP) 技術,對曝光形成的圖形進行薄膜沉積和蝕刻,使圖形密度達成翻倍,在此基礎上完成 10 奈米線寬的奈米壓印技術。公司稱,本次研發不僅利用了其在光罩製造領域長期積累的高精度圖形化能力,還結合了晶圓製造製程技術,進一步在產品精度、穩定性與可量產性方面滿足先進邏輯半導體的要求。根據公司推測,採用奈米壓印的超精細半導體製程技術,可將曝光環節的能源消耗降至當前主流製程的大約 1/10。

在產業化推進方面,DNP 已與半導體製造商開展溝通,並啟動新型 NIL 奈米壓印技術的評估工作。公司計畫在完成客戶驗證、建立量產製程和供應體系後,於 2027 年開啟量產供貨,以應對邏輯半導體微縮帶來的市場需求。DNP 表示,將持續推動奈米壓印技術升級和產能擴充,以匹配未來市場放量節奏,將相關業務培育為公司半導體板塊的重要增長關鍵點。

此外,DNP 還計畫在 2025 年 12 月 17 日至 19 日於東京國際展覽中心舉辦的 SEMICON Japan 2025 上,展出這款 10 奈米線寬 NIL 奈米壓印技術。公司認為,通過在專業展會集中展示產品與技術路線,可加深與全球半導體製造企業及設備廠商的交流,推動奈米壓印技術在先進邏輯制程中的應用發展。後續該技術在量產良率、生產節拍以及與既有製程技術整合方面的表現,將成為市場持續關注的重點。

(首圖來源:DNP)