全球半導體大廠英特爾 (Intel) 日前大型舉辦展示,揭露其在先進封裝領域的最新研發成果,推出一系列以 Intel 18A 與 Intel 14A 等先進節點製程的多小晶片(Multi-chiplet)產品概念。此次展示不僅展現了英特爾在 Foveros 3D 與 EMIB-T 先進封裝技術上的突破,更傳遞出其希望在高效能運算(HPC)、人工智慧(AI)及資料中心市場,與台積電的 CoWoS 封裝技術一決高下的強烈企圖心。

英特爾本次技術展示的核心在於其精密,且具高度擴展性的先進封裝架構。根據資料顯示,英特爾將利用 Intel 14A-E 節點製程提供突破性的邏輯效能,該製程同時採用了 RibbonFET 2 與 PowerDirect 技術。而在基礎晶片部分,則採用 Intel 18A-PT 製程,這是首款採用背後供電技術的基礎晶片,能顯著提升邏輯密度與電力供應的可靠性。

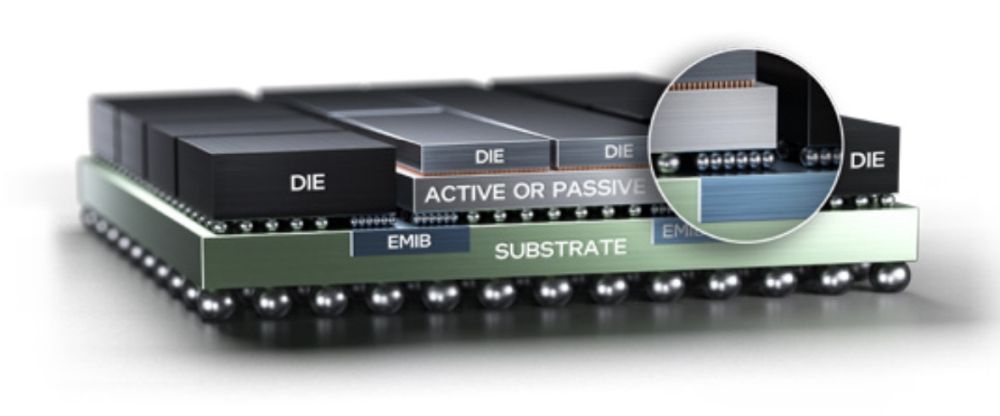

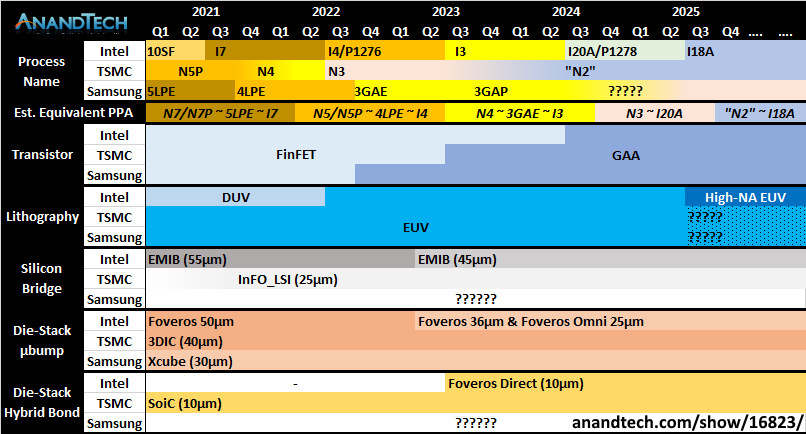

此外,為了達到極致的垂直堆疊目標,英特爾還導入了 Foveros Direct 3D 技術,透過極細間距的混合鍵合(Hybrid Bonding)進行精密 3D 堆疊。而在多晶片互連方面,新一代的嵌入式多晶片互連橋接(EMIB-T)技術加入了矽穿孔(TSV)技術,可提供更高的頻寬,並整合更大規模的晶片組。

另外,英特爾還在展示影片中揭露了兩款極具前瞻性的概念設計,展現了其超越傳統光罩限制(Reticle Limit)的技術實力。其中在中階解決方案方面,可配備 4 個運算晶片與 12 個 HBM 位點。至於在旗艦解決方案方面,則是規模擴大到 16 個運算晶片與 24 個 HBM 位點,並可配置多達 48 個 LPDDR5X 控制器,極大化 AI 與資料中心工作執行所需的記憶體密度。

而且,這些設計採用了類似「Clearwater Forest」的架構,其基礎晶片負責搭載 SRAM,並透過 Foveros 3D 技術將頂層包含 AI 引擎或 CPU IP 的運算晶片堆疊在上面。記憶體支援方面,英特爾強調其封裝方案能無縫兼容目前的 HBM3/HBM3E,以及未來的 HBM4、HBM5 等次世代標準。

根據市場的分析,英特爾這次一系列展示動作,無疑是向台積電發出挑戰。台積電目前已規劃 9.5 倍光罩尺寸的 CoWoS 解決方案,並結合 A16 製程,以及超過 12 個 HBM4E 位點(CoWoS-L)。然而,英特爾表示,其封裝架構具備超過 12 倍的光罩尺寸,顯示在規格上有意超越對手。英特爾還特別強調,雖然 Intel 18A 製程主要用於其內部產品,但 intel 14A 節點製程則是專為外部客戶設計的。因此,英特爾目前正積極與產業夥伴建立多元生態系,目的是提供更快的上市時間與更具韌性的供應鏈。

儘管英特爾過去在先進封裝領域早有建樹,例如被視為工程奇蹟的 Ponte Vecchio 晶片,但受限於良率問題與研發延遲,該產品並未取得商業化上的成功,隨後如 Falcon Shores 等多項計畫也遭取消。因此,目前英特爾正試圖憑藉 Jaguar Shores,以及備受期待的 Crescent Island AI GPU 捲土重來。對英特爾而言,真正的考驗在於能否成功爭取到第三方客戶的訂單。尤其在 Intel 14A 技術與先進封裝解決方案的加持下,英特爾似乎已準備好重新回歸晶圓代工市場的頂尖賽局。

(首圖來源:英特爾提供)