面對半導體產業從消費性電子驅動轉向高效能運算(HPC)驅動的結構性變革,聯發科(MediaTek)正積極部署下一代資料中心關鍵技術。聯發科總經理暨營運長陳冠州明確指出,公司正全力投入矽光子(Silicon Photonics)與共同封裝光學(CPO)技術的研發,並將其視為未來最重要的技術投資方向之一。

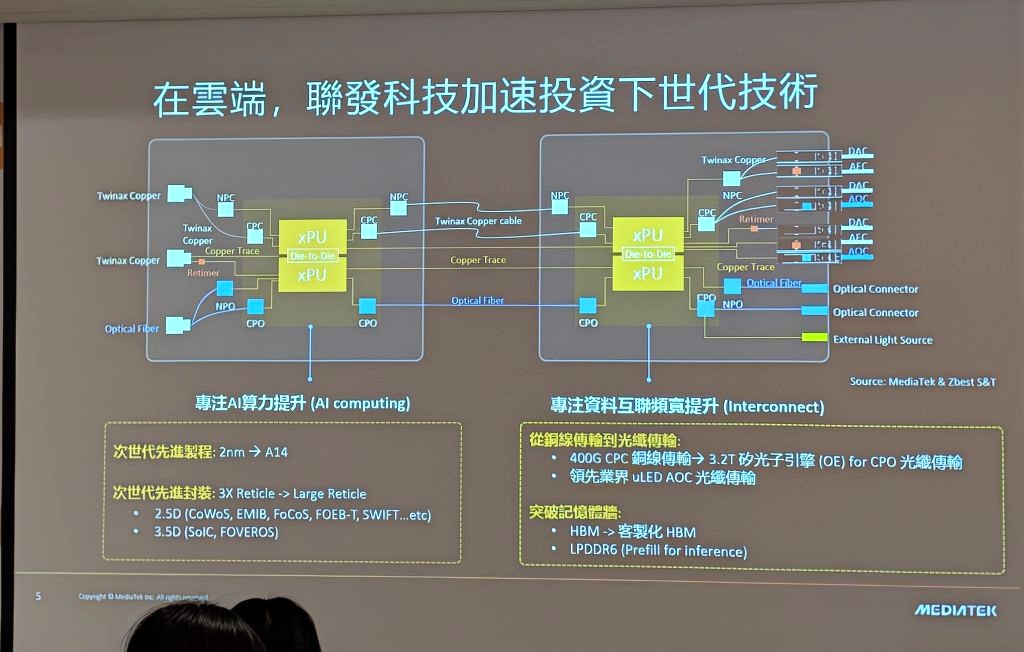

陳冠州指出,隨著雲端運算與 AI 模型的規模呈指數級增長,資料中心的傳輸速率需求急劇上升。聯發科指出,公司在雲端技術的佈局共有三大核心,其中「由電轉光」的趨勢已不可逆。目前聯發科在 SerDes(序列解序列器)技術上已推進至 200G,2026 年更會有 400G 的 IP 案子問世。然而,隨著傳輸速率不斷提升,傳統銅線傳輸面臨物理極限。聯發科管理層強調,在 400G 之後,技術發展勢必會走到「光」的領域,這是公司非常重要的投資方向。

針對市場高度關注的矽光子發展路徑,陳冠州明確表示,共同封裝光學(CPO,Co-Packaged Optics)是確定的技術演進方向。CPO 技術能將光引擎與運算晶片緊密封裝在一起,大幅縮短電訊號傳輸距離,進而降低功耗並提升訊號品質。

至於,矽光子的具體應用場景,陳冠州則是透露,目前的焦點在於「XPU 與 XPU 之間的連接」。在龐大的資料中心內,數以萬計的運算單元(XPU)需要進行高速資料交換,這正是聯發科認為對其而言最重要的切入點。而除了長距離傳輸,光通訊技術也開始影響機櫃內部的短距連接。聯發科預告,將在2026年四月的光纖通訊大會(OFC)上,展示利用 Micro-LED 技術實現的主動式光纜(AOC)新型態解決方案。這顯示聯發科不僅佈局長遠的 CPO,在近期的光通訊應用上也已有具體成果準備推向市場。

陳冠州強調,矽光子技術的實現並非僅靠單一晶片,而是涉及高度複雜的整合工程。聯發科解釋,光通訊技術的重點在於如何將光積體電路(PIC)與電積體電路(EIC)進行完美的封裝與整合,這直接連結到先進封裝技術的挑戰。聯發科指出,無論是 2.5D 或 3D 封裝,當晶片堆疊時,電性干擾與散熱特性與傳統消費性電子產品截然不同,挑戰非常巨大。為了克服這些障礙,聯發科已與台積電建立緊密合作關係,利用台積電的 COUPE (Compact Universal Photonic Engines) 平台來實踐先進封裝的光學技術。

聯發科強調,雖然業界存在不同的技術路線,且各自有優缺點,但公司抱持開放態度,會根據客戶產品的特性(適合 A 技術或 B 技術)來協助客戶完成設計,並不侷限於單一方案。儘管目前先進封裝產能(CoWoS)相當吃緊,聯發科表示已確認能取得滿足2026年及2027年目標所需的產能。公司在先進製程與先進封裝的供應鏈佈局上,除了台積電外,尚未有新的主要合作夥伴。

為了支撐龐大相關技術研發需求,聯發科也將持續加大投資規模。這包括內部資源的重新分配與組織調整,以及積極招募具備系統架構能力的 HPC 專才,招聘範圍更延伸至美國等地。針對 2026 年的投資規劃,聯發科預期將會有相當幅度的成長。雖然手機市場在 2026 年可能面臨挑戰,但受惠於資料中心、ASIC 及 AI 相關業務的強勁需求,公司對於整體營運前景仍具信心,並致力於協助客戶在不同價格帶的產品上進行資源調配與避險。

陳冠州進一步指出,正透過深耕 SerDes、矽光子、CPO 及先進封裝技術,企圖在 AI 資料中心基礎建設中佔據關鍵地位,並將此技術紅利延伸至邊緣運算裝置,以此擺脫純消費性電子市場的波動,轉型為以 HPC 為核心驅動力的全方位半導體領航者。

(首圖來源:科技新報攝)