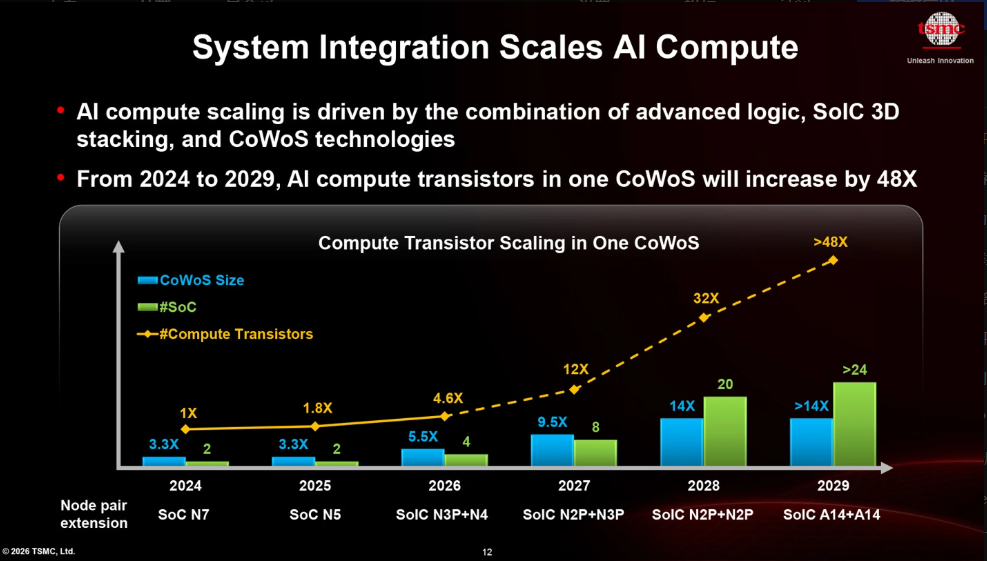

隨著 AI 與高效能運算 (HPC) 對晶片效能的要求日益嚴苛,先進封裝技術已成為驅動效能升級的關鍵引擎。台積電於 2026 年北美技術論壇上公布了最新的 SoIC 3D 封裝技術藍圖,宣布將於 2029 年進一步縮小互連間距,並推出 A14 對 A14的 SoIC 堆疊技術,展現其在先進封裝領域的強大企圖心。

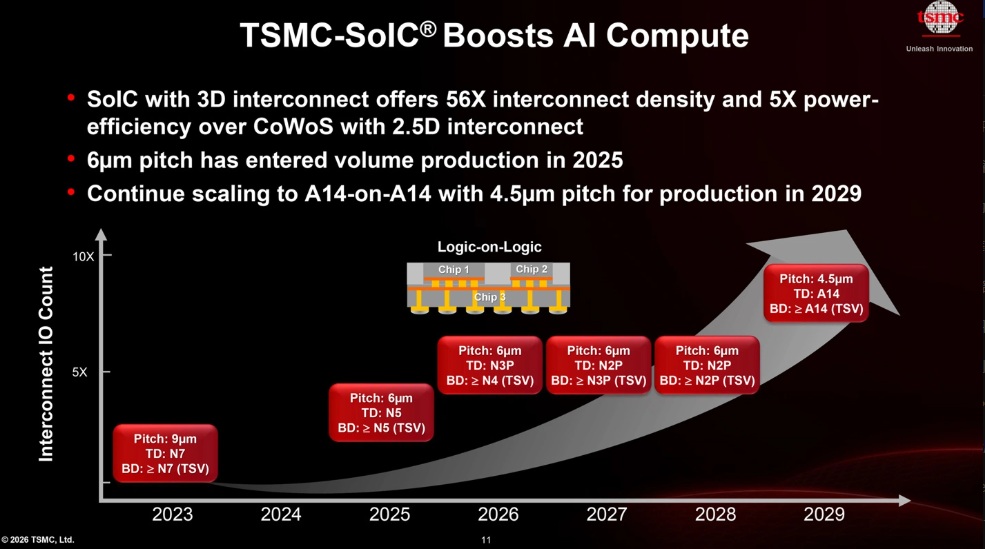

根據台積電最新公布的技術藍圖,SoIC 的互連間距將從目前的 6 微米 (µm),在 2029 年大幅縮小至 4.5 微米。這項間距微縮技術對於混合鍵合晶片堆疊至關重要,因為它直接決定了晶片間能容納的垂直互連數量。台積電指出,預計 2029 年投入量產的 A14 對 A14的 SoIC 技術,其晶片對晶片的 I/O 密度將比 N2 對 N2的 SoIC 提升 1.8 倍。

SoIC 隸屬於台積電 3DFabric 先進封裝家族,目的在透過超高密度的垂直堆疊技術來縮小晶片體積、提升整體效能,並降低電阻、電感與電容。而此次技術藍圖中的核心變革,是從傳統的面對背 (face-to-back) 轉向面對面 (face-to-face) 堆疊。在面對背設計中,訊號必須穿越較複雜的路徑 (包含底層晶片的矽穿孔)。而在面對面堆疊中,兩顆晶片的主動金屬層可以直接對齊,並透過混合銅鍵合技術連接,大幅縮短了晶片間的傳輸路徑。

根據博通 (Broadcom) 的實際測試數據,面對面堆疊的訊號密度可達每平方毫米 14,000 個訊號,遠超過面對背堆疊的 1,500 個訊號。這項躍進帶來了更高的頻寬與更低的延遲,儘管業界仍需持續克服隨之而來的製造與散熱挑戰。而台積電的高密度晶片堆疊技術已開始進入實戰階段,富士通 (Fujitsu) 專為 AI 與 HPC 工作負載設計的 Monaka 處理器,預期將成為首批受惠於面對面晶片堆疊技術的系統之一。

另外,博通於 2026 年 2 月宣布,已開始出貨結合 2.5D 整合與 3D-IC 面對面堆疊技術的 3.5D XDSiP 平台,並以此打造 2 奈米客製化運算 SoC 供 Monaka 計畫使用,讓運算、記憶體與網路 I/O 得以在緊湊的封裝中獨立擴展。該處理器預計於 2027 年問世,屆時將可驗證高密度的面對面堆疊技術是否已具備商業量產的經濟效益。

根據外媒報導,這份 SoIC 藍圖呼應了整體半導體產業的趨勢轉變。隨著先進製程微縮變得日益昂貴且困難,晶圓代工廠與晶片設計商正將提升效能的重心轉移至先進封裝上,包含更大的中介層、更密集的晶片連結、堆疊快取及 HBM 整合等。雖然考量到成本、良率、散熱限制及設計複雜度,台積電 2029 年的目標並不代表所有先進處理器都會全面採用最高密度的 SoIC 方案。但此藍圖明確宣示,台積電已將垂直整合視為其先進製程策略中的核心支柱,而非僅僅是利基型的封裝選項。

(首圖來源:官網)